# PCI Express Time and Frequency Processor

bc635PCle

Time is typically acquired from time code signals such as IRIG B. Extensive time code generation and translation are both supported. The translator reads and disciplines the internal oscillator to either the amplitude modulated (AM) and DC level shift (DCLS) formats of IRIG A, B, G, E, IEEE 1344, NASA 36, XR3, or 2137 time codes. The generator outputs are either IRIG A, B, G, E, IEEE 1344, NASA 36, XR3, or 2137 in both AM and/or DCLS formats.

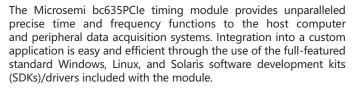

Central to the operation of the module is a disciplined 10 MHz oscillator that is either a TCXO or optional OCXO that provides the timing module a 100 ns clock. Current time (days to 100 ns) can be accessed across the PCIe bus with no PCIe bus wait states, which allows for high speed, low latency time requests. The 10 MHz oscillator drives the module frequency and time code generator circuitry. If the input reference is lost, the module continues to maintain time (flywheel) based on the 10 MHz oscillator's drift rate. The optional OCXO oscillator improves flywheel drift performance over the standard TCXO. If power is lost, a battery backed real-time clock (RTC) maintains the time. The module has a state-of-the-art direct digital synthesizer (DDS) rate synthesizer with a range from 0.0000001PPS to 100MPPS. The module may also be programmed to generate an interrupt at a precise predetermined time based on a time compare (strobe). Three event time capture inputs provide a means of latching time of different external events.

A key feature of the bc635PCIe is the ability to generate interrupts on the PCIe bus at programmable rates. These interrupts can be used to synchronize applications on the host computer as well as signal specific timing events over the bus.

The external frequency input is a unique feature allowing the time and frequency of the bc635PCle to be derived from an external oscillator that may also be disciplined (DAC voltage controlled) based on the selected input reference. The module may be operated in generator (undisciplined) mode where an external 10 MHz from a Cesium or Rubidium standard is used as the frequency reference. This creates an extremely stable PCle-based clock for all bc635PCle timing functions.

Integration of the module is easily facilitated with the included SDKs/drivers for 32/64-bit Windows and Linux, and 64-bit Solaris.

### **KEY FEATURES**

- IRIG A, B, G, E, IEEE 1344, NASA 36, XR3, and 2137 time code inputs and outputs

- Simultaneous AM and DCLS time code inputs and outputs

- 100 ns clock resolution for time requests

- Programmable <<1PPS to 100MPPS DDS rate synthesizer output/interrupt</li>

- 1, 5, or 10MPPS rate generator output

- 1PPS and 10 MHz inputs

- Three external event time capture/interrupts

- Programmable time compare output/interrupt

- Zero latency time reads

- Battery backed real-time clock (RTC)

- Low-profile PCle form factor

- Linux, Solaris, and Windows software drivers/SDKs included

- Superior user interface and documentation

- Optional OCXO upgrade

#### **KEY BENEFITS**

- Precise sub-microsecond time available to host computer applications

- Easy integration facilitated by included Windows, Linux, and Solaris SDKs and drivers

- Extremely fast time reads

- Programmable time and frequency functions to quickly customize for specific applications

- Wide variety of time codes facilitate easy integration with existing systems

- Dedicated and responsive technical support to assist in PCIe card integration

- Well documented for easy and fast system integration

# Precision Time and Frequency in the PCle Form Factor (100-Nanosecond Precision, TCXO or OCXO Oscillators

#### Inputs

- · AM time codes

- DCLS time codes

- External events (3x)

- 10 MHz

- 1PPS

- GPS (bc637PCle model)

#### **Outputs**

- AM time codes

- · DCLS time codes

- Programmable alarm (strobe/time compare)

- <<1PPS to 100MPPS rates</li>

- 1PPS

- 1, 5, or 10MPPS

- Oscillator control voltage

# Over the PCIe Bus Precise time

- Event interrupts

- Alarm interrupts (time compare/strobe)

- Programmable interrupt rates

- Configuration and control

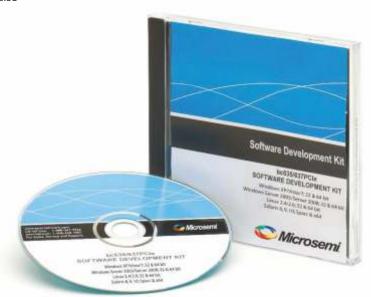

# **Reading the Precise Time**

The bc635PCle provides precise time on request and extremely fast response to host applications. This request for time is made using the included SDK software functions. Time can be provided in binary or decimal form.

### A Multitude of Time Codes

The bc635PCIe has the widest time code input and output support available in any bus level timing card. Support is available for 30 different time codes, including IRIG A, B, G, E, IEEE 1344, NASA 36, XR3, and 2137 in AM and DCLS formats.

#### **Measure External or Internal Events**

Measure the exact time up to the occurence of three independent external events. Bus interrupts instantly notify the CPU that the measurements are made and waiting. Similarly, host application generated interrupts to the bc635PCle card over the bus can be precisely time stamped for precise host application-based processes.

#### **Flexible Rate Generation**

The DDS on the bc635PCle can be programmed to generate rates up to 100MPPS or as little as once every 115 days. These rates are available as timing signal outputs or as interrupts on the bus. The rate adjustment resolution is as small as 1/32 Hz.

# **Frequency Outputs**

Precise clocks are excellent sources of frequency outputs. The bc635PCle offers 1, 5, or 10MPPS outputs directly from the steered internal oscillator of the clock.

# **External Frequency Inputs and DAC Control**

The external frequency input is an unique feature that allows the time and frequency of the bc635PCle to be derived from an external oscillator such as a 10 MHz Cesium or Rubidium standard. This creates an extremely stable PCle-based clock for all bc635PCle timing functions. For closed loop control, an external oscillator may be disciplined using DAC voltage control output from the bc635PCle.

### Time Compare/Strobe/Alarm

A useful feature of any precise clock is the ability to notifiy when a particular time is reached (like an alarm clock). When the preset time precisely matches the actual time, an external signal and an interrupt to the bus are instantly generated, signaling an application that point in time has just occurred.

#### **Over-the-Bus Features**

Beside from precise time stamps, the bc635PCle can provide very precisely timed interrupts on the bus at fixed rates, predetermined times, or to signal an event has occurred on the card. These interrupts can be integrated into user applications requiring more deterministic behavior or application synchronization with other computers. Similarly, user applications can use interrupts as markers in time and later retrieve exactly when the interrupt occurred.

# **Configuration and Control**

The bc635PCle includes easy-to-use programs to easily configure the card and validate operations. This software is also included with the SDKs and driver software.

# PCIe Card Integration Made Easy with Included SDKs and Drivers

# Windows, Linux, and Solaris SDKs Speed PCIe Integration

The PCIe card includes standard full-featured software development kits, speeding the integration of Microsemi PCIe cards into any application.

Using an SDK is an easy-to-integrate and highly reliable alternative to writing lower-level code to address a card's memory registers directly with just a driver. The function calls and device drivers in the SDKs make interfacing to a Microsemi PCIe card straightforward and help keep the software development focused on the end application.

# **SDKs Save Time and Money**

Programmers find the SDK an invaluable resource in accelerating the integration of Microsemi PCIe cards into applications, saving both time and money. The SDK functions address each Microsemi PCIe timing card feature, and the function names and parameters provide insight into the capability of each function. By using the SDK, one can leverage Microsemi's timing expertise and confidently integrate a Microsemi PCIe card into your application.

#### License-Free

Distribution of embedded Microsemi software in customer applications is royalty free.

# **Driver Comparison**

#### Windows SDK and Driver

- Windows XP/Vista/7/10

- Windows Server 2003/2008

- 32- and 64-bit support

- Kernel mode driver

- Code examples

- Test application program

- Complete documentation

- Timekeeping utility program

The Windows SDK for bc635PCle cards include a Windows XP/Vista/Server/7/10 kernel mode device driver for the 32- and 64-bit PCle interface. The SDK includes .h, .lib, and DLL files to support both 32- and 64-bit application development.

The target programming environment is Microsoft Visual Studio (Microsoft Visual C++ V6.0 or higher). Both Visual C++ 6.0 and Visual Studio 2008 project files are supplied with the source code

Also included is Microsemi's bc637PClcfg application program that can be used to ensure proper operation of the PCle card, and the TrayTime application that allows the user to update the system clock in which the card is installed. Source code for these programs and smaller example programs are included.

**Minimum System Requirements**

#### **Operating System**

- Windows XP/Vista/7/10

- Windows server 2003/2008

#### Hardware

PC-compatible system with a Pentium or faster processor

Memory

24 MB

#### **Development Environment**

Microsoft Visual Studio (Visual C++) 6 or higher

#### **Linux SDK and Driver**

- Up to Linux Kernel 4.6

- 32- and 64-bit kernel support

- Code examples

- Test application program

- Complete documentation

The Linux SDK for bc635PCle cards includes PCle kernel mode device drivers for both 32-bit and 64-bit kernels, an interface library accessing all bc635PCle features, and example programs with the source code.

The target programming environment is the GNU compiler collection (GCC) and the C/C++ programming languages.

Also included is Microsemi's bc63xPClcfg application program, which ensures proper operation of the PCle card in the host computer. The example program includes sample code, exercising the interface library, and conversion examples of the ASCII format data objects passed to and from the device into a binary format suitable for operation and conversion. The example program is developed using discrete functions for each operation, allowing the developer to copy any useful code and use it in their own applications.

**Minimum System Requirements**

#### **Operating System**

Linux Kernels 3.10

#### Hardware

x86 processor

#### Memory

32 MB

### **Development Environment**

GNU GCC recommended

#### **Solaris SDK and Driver**

- Solaris kernel mode driver

- 64-bit Solaris 8–10

- Code examples

- Test application program

- Complete documentation

Microsemi's Solaris SDK includes bc63xPClcfg, an application program to ensure proper operation of the PCle card in the host computer. The example program includes sample code and conversion examples of the ASCII format data objects passed to and from the device into a binary format suitable for operation and conversion.

The target programming environment is the Solaris application development tool chain and the C/C++ programming languages.

The Solaris SDK includes the Solaris device driver source code. Applications access the features of the hardware through the standard 'ioctl' Solaris system function. The ioctl codes are defined for all the features of the card. The bc63xPClcfg program shows how to use most ioctl codes. Developers can copy any useful code from the bc63xPClcfg source code and use it in their own applications.

**Minimum System Requirements**

### **Operating System**

Solaris versions 8, 9, and 10

#### Hardware

SPARC and x86\_64

#### Memory

32 MB

# **Development Environment**

Solaris compilers

# Windows and Linux SDK Function Reference

Note: For complete list of functions, see the manual.

**Basic Time and Frequency Processor (TFP) Functions**

• bcStartPCI/bcStopPCI Opens/closes underlying device layer.

• bcStartInt/bcStopInt Starts/stops the interrupt thread to signal interrupts.

bcSetInt/bcReqInt Enables/returns enabled interrupt.

bcShowInt Interrupt service routine.

bcReadReg/

bcWriteReg.

Returns/sets requested register contents.

bcReadDPReg/

bcWriteDPReg

Returns/sets requested dual port

RAM register contents.

• bcCommand Sends SW reset command to board.

• bcReadBinTime/ Reads/sets TFP major time in brSetRinTime binary format.

bcReadDecTime/

bcSetDecTime

Reads/sets TFP major time in BCD format.

bcReqTimeFormat

bcSetTimeFormat

Sets the major time format to binary or grouped decimal.

bcReqYear/bcSetYear

bcSetYearAutoIncFlag

Included for backward compatibility to the bc635/637PCI-U card.

• bcSetLocalOffsetFlag Enables or disables local time offset in conjunction with bcSetLocOff.

bcSetLocOff

Sets board to report time at an offset relative to UTC.

(in non-GPS modes)bcSetMode Sets TFP operating mode.

• bcSetTcIn Sets time code format for time code decoding mode

• bcSetTcInEx Sets time code and subtype for

bcSetTcInMod time code decoding mode.

bcSetTcInMod Sets time code modulation for time code decoding mode.

• bcReqTimeData Returns selected time data from the board.

bcReqTimeCodeData

Returns selected time code data from the board.

• bcReqTimeCodeDataEx Returns selected time code and subtype data from the board.

bcReqOtherData

Returns selected data from the

bcReqVerData

Returns firmware version data from the board.

• bcRegSerialNumber Returns board serial number.

• bcReqHardwareFab Returns hardware fab part number.

bcReqAssembly

Returns assembly part number.

Detailed TER model identification.

bcReqModel Returns TFP model identification.

bcReqTimeFormat Returns selected time format.

• bcReqRevisionID Returns board revision.

**Event Functions**

bcReadEventTime

Latches and returns TFP time

caused by an external event

• bcReadEventTimeEx Latches and returns TFP time caused by an external event with

100 ns resolution.

• bcSetHbt Sets a user programmable

periodic output.

bcSetPropDelay

Sets propagation delay

compensation.

• bcSetStrobeTime Sets strobe function time.

• bcSetDDSFrequency Sets DDS output frequency.

• bcSetPeriodicDDSSelect Selects periodic or DDS output.

• bcSetPeriodicDDSEnable Enables or disables periodic or

DDS output.

bcSetDDSDivider

bcSetDDSDividerSource

Sets DDS divider value.

Sets DDS divider source.

• bcSetDDSSyncMode Sets DDS synchronization

mode.

bcSetDDSMultiplier Sets DDS multiplier value.bcSetDDSPeriodValue Sets DDS period value.

• bcSetDDSTuningWord Sets DDS turning word value.

**Oscillator Functions**

bcSetClkSrc

Enables or disables on-board

oscillator.

bcSetDac

Sets oscillator DAC value.

bcSetGain

Modifies on-board oscillator frequency control algorithm.

• bcReqOscData Returns TFP oscillator data.

**Generator Mode Functions**

• bcSetGenCode Sets time code generator format.

• bcSetGenCodeEx Sets time code and subtype

generator format.

• bcSetGenOff Sets an offset to the on-board

timecode generation function.

**GPS Mode Functions**

bcGPSReq/ bcGPSSnd Returns/sends a GPS receiver

data packet.

bcGPSMan Manually send and retrieve GPS

receiver data packets.

• bcSetGPSOperMode Sets the GPS receiver to function

in static or dynamic mode.

bcSetGPSTmFmt

Sets TFP to use GPS or UTC time

base.

Real-Time Clock (RTC) Functions

• bcSyncRtc Synchronizes RTC to current TFP

time.

bcDisRtcBatt

Sets RTC circuit and battery to

disconnect after power is turned

off.

#### Solaris SDK Function Reference

The Solaris SDK uses custom ioctl commands to facilitate easy communication and control of the bc635PCle card. The commands cover basic operational functions, event management, oscillator controls, and mode-related functions.

The following list is an overview of the Solaris SDK's ioctl functions.

- · Interrupt management

- Read/write dual port RAM. Send command to timing engine for processing

- Read and write time

- Timing mode and time format

- · Read and write the card control register

- Input time code format and modulation selection

- Set local time

- Leap seconds control

- Read various version information and miscellaneous data

- Reset the board

- Clock source and JamSync management

- DAC control

- On-board oscillator frequency control

- Advance or retard the internal clock

- Read event time latched by external event

- Read event time latched by software event

- Event source/sense control

- Set propagation delay

- · Periodic output and output frequency control

- · Strobe control

- DDS frequency output control

- · Set output time code format

- Set offset for output time code generation

- · GPS control

- Sync real time clock

- Disconnect between RTC and battery after power off

# **Backward Compatibility Provides Seamless Migration Paths**

The PCI-based bc635 cards have long product lifecycles since the first introduction of PCI timing cards in the mid 1990s. To preserve the customer's time and money investments in integrating bc635PCI cards into their systems, Microsemi has maintained the bc635PCI cards' existing features and software interface while adding new features and keeping their bus signaling and form factors up to date. This commitment to backward compatibility and current bus architectures assures the bc635PCI cards integrate smoothly into any workstation currently available in the market with little to no impact on customer application software.

### bc635PCI

Mid-1990s

First PCI timing card introduced

#### bc635PCI-U

2003

3.3 V and 5.0 V universal signaling backward compatibility retained

#### bc635PCI-V2

2008

Electronics updated backward compatibility retained

- 2009

- PCIe supported backward compatibility retained

# **Optional Accessories Speed, Test, and Simplify Integration**

Breakout cables with BNC connectors simplify access to the in and out timing signals of the PCIe card. These labeled cables mitigate the need to create special cables during project development and ensure that the correct timing signals are being accessed.

For more integrated rack mount systems that require easy access to timing signals, the 1U patch panel and high-frequency signal breakout exposes all available signals. The panel provides an organized and professional appearance to the external timing I/O of the PCle card functions. The 1U panel fits with standard or half rack size chassis. The high-frequency breakout adapter exposes the high-frequency signal as well as the external DC DAC control signal and ground.

# Input/Output Signals D to BNC Connector Breakout Cables

| Timing Input/Output Breakout<br>Cable and Patch Panel BNC Map | D to 5-BNC<br>(BC11576-1000) | D to 5-BNC<br>BC11576-9860115 | D to 6-BNC | atch/Breakout |

|---------------------------------------------------------------|------------------------------|-------------------------------|------------|---------------|

| Outputs                                                       |                              |                               |            |               |

| Time code (AM)                                                | •                            | •                             | •          | •             |

| Time code (DCLS)                                              |                              |                               | •          | •             |

| 1, 5, or 10MPPS                                               |                              |                               |            | •             |

| Periodic/DDS                                                  |                              |                               |            | •             |

| Strobe                                                        |                              |                               |            | •             |

| 1PPS                                                          | •                            | •                             | •          | •             |

| Oscillator control voltage                                    |                              |                               |            | •             |

| Inputs                                                        |                              |                               |            | •             |

| Time code (AM)                                                | •                            | •                             | •          | •             |

| Time code (DCLS); event2                                      |                              |                               |            | •             |

| External event1                                               | •                            | •                             | •          | •             |

| External 1PPS; event3                                         |                              | •                             | •          | •             |

| External 10 MHz                                               |                              |                               |            | •             |

1U Patch Panel of Input/Output and High Frequency Signals for Standard Rack Mount Size Chassis

# **Specifications**

| Electrical                    |                                                                     |  |  |  |

|-------------------------------|---------------------------------------------------------------------|--|--|--|

| Real-time clock               |                                                                     |  |  |  |

| Bus request resolution        | 100 ns                                                              |  |  |  |

| Latency                       | Zero                                                                |  |  |  |

| Major time format             | Binary or BCD                                                       |  |  |  |

| Minor time format             | Binary                                                              |  |  |  |

| Synchronization sources       | Time code, 1PPS                                                     |  |  |  |

| Time code translator (inputs) |                                                                     |  |  |  |

| Time code formats             | IRIG A, B, G, E, IEEE                                               |  |  |  |

|                               | 1344, NASA 36, XR3, 2137                                            |  |  |  |

| Time accuracy                 | <5 μS (AM carrier frequencies                                       |  |  |  |

|                               | 1 kHz or greater)                                                   |  |  |  |

|                               | <1 μS (DCLS)                                                        |  |  |  |

| AM ratio range                | 2:1 to 4:1                                                          |  |  |  |

| AM input amplitude            | 1 V <sub>pp</sub> to 8 V <sub>pp</sub>                              |  |  |  |

| AM input impedance            | >5 kΩ                                                               |  |  |  |

| DCLS input, event2            | 5 V HCMOS >2 V high,                                                |  |  |  |

| Decompany events              | <0.8 V low                                                          |  |  |  |

| Time code generator (output   | ***                                                                 |  |  |  |

| Time code format              | IRIG A, B, G, E, IEEE 1344,                                         |  |  |  |

|                               | NASA 36, XR3, 2137                                                  |  |  |  |

| AM ratio                      | 3:1 ±10%                                                            |  |  |  |

| AM amplitude                  | $3.5 \text{ V}_{pp} \pm 0.5 \text{ V}_{pp} \text{ into } 50 \Omega$ |  |  |  |

| DCLS amplitude                | 5 V HCMOS, >2 V high,                                               |  |  |  |

| DCLS amplitude                | <0.8 V low into 50 Ω                                                |  |  |  |

| Timing functions (outputs are |                                                                     |  |  |  |

| DDS rate synthesizer          |                                                                     |  |  |  |

| Frequency range               | 0.0000001PPS to 100MPPS                                             |  |  |  |

| Output amplitude              | 5 V HCMOS, >2 V high,                                               |  |  |  |

|                               | $< 0.8 \text{ V low into } 50 \Omega, \text{ square}$               |  |  |  |

|                               | wave                                                                |  |  |  |

| Jitter                        | <2 nS p-p                                                           |  |  |  |

| Legacy pulse rate synthesizer |                                                                     |  |  |  |

| Frequency range               | <1 Hz to 250 kHz                                                    |  |  |  |

| Output amplitude              | 5 V HCMOS, >2 V high,                                               |  |  |  |

|                               | $< 0.8 \text{ V low into } 50 \Omega$ , square                      |  |  |  |

|                               | ·                                                                   |  |  |  |

| Time compare (strobe)         | wave                                                                |  |  |  |

| Compare range                 | 1 μs through days                                                   |  |  |  |

| Output amplitude              | 5 V HCMOS, >2 V high,                                               |  |  |  |

|                               | <0.8 V low into 50 Ω, 1 μs                                          |  |  |  |

|                               | pulse                                                               |  |  |  |

| 1PPS output                   | 5 V HCMOS, >2 V high,                                               |  |  |  |

|                               | <0.8 V low into 50 Ω, 60 μs                                         |  |  |  |

|                               | pulse                                                               |  |  |  |

| 1PPS input, event3            | 5 V HCMOS, >2 V high,                                               |  |  |  |

| l                             | <0.8 V low                                                          |  |  |  |

| External event input          | 5 V HCMOS, >2 V high,                                               |  |  |  |

|                               | <0.8 V low, zero latency                                            |  |  |  |

| External 10 MHz oscillator    | Digital 40% to 60% or sine                                          |  |  |  |

|                               | wave, 0.5 Vpp to 8 Vpp,                                             |  |  |  |

|                               | >10 kΩ                                                              |  |  |  |

|                               | > 10 K22                                                            |  |  |  |

| Oscillator control voltage     | Jumper selectable<br>0 VDC-5 VDC or<br>0 VDC-10 VDC                                                |  |

|--------------------------------|----------------------------------------------------------------------------------------------------|--|

| On-board disciplined oscillate | or                                                                                                 |  |

| Frequency 10 MHZ               |                                                                                                    |  |

| 1, 5, or 10 MHz output         | 5 V HCMOS, >2 V high,<br><0.8 V low into 50 Ω                                                      |  |

| Stability                      |                                                                                                    |  |

| Standard TCXO                  | 5.0×10 <sup>-8</sup> short term<br>"tracking" 5.0×10 <sup>-7</sup> /day<br>long term "flywheeling" |  |

| Optional OCXO                  | 2.0×10 <sup>-9</sup> short term<br>"tracking" 5.0×10 <sup>-8</sup> /day<br>long term "flywheeling" |  |

| Real-time clock (RTC)          | Battery backed time and year information                                                           |  |

| PCIe specification             | Single lane PCIe interface, r1.0a compatible                                                       |  |

| Size                           | Standard height<br>low-profile PCIe                                                                |  |

| Power                          | 3.3 V at 400 mA<br>12 V at 250 mA (TCXO),<br>350 mA (OCXO)                                         |  |

| Connector                      |                                                                                                    |  |

| Timing I/O                     | 15-pin DS software                                                                                 |  |

| Environmental                  |                                                                                                    |  |

| Temperature                    |                                                                                                    |  |

| Operating                      | 0 °C to 70 °C                                                                                      |  |

| Storage                        | −30 °C to 85 °C                                                                                    |  |

| Humidity                       |                                                                                                    |  |

| Operating                      | 5% to 95% non-condensing                                                                           |  |

| Operating altitude             | Up to 18,000 m MSL                                                                                 |  |

| Certifications                 |                                                                                                    |  |

| FCC                            | Part 15, Subpart B.                                                                                |  |

| CE                             | Emissions EN 55022                                                                                 |  |

| Immunity                       | EN 55024                                                                                           |  |

| RoHS compliance                |                                                                                                    |  |

| EU RoHS 6/6<br>China RoHS      |                                                                                                    |  |

### **Pin Description**

| Pin | Direction | Signal                     |

|-----|-----------|----------------------------|

| 1   | Input     | External 10 MHZ            |

| 2   |           | Ground                     |

| 3   | Output    | Strobe                     |

| 4   | Output    | 1PPS                       |

| 5   | Output    | Time code (AM)             |

| 6   | Input     | External event1            |

| 7   | Input     | Time code (AM)             |

| 8   |           | Ground                     |

| 9   | Output    | Oscillator control voltage |

| 10  | Input     | Time code (DCLS); event2   |

| 11  | Output    | Time code (DCLS)           |

| 12  |           | Ground                     |

| 13  | Output    | 1, 5, or 10MPPS            |

| 14  | Input     | External 1PPS; event3      |

| 15  | Output    | Heartbeat/DDS              |

**Pin Diagram**

bc635PCle Low-Profile and Standard Cover Panels

#### **Software**

the 32/64-bit versions of Windows and Linux, and 64-bit Solaris. Included are test application programs with source code so that you can review the bc635PCIe card status and adjust board configuration and output parameters. Each SDK includes an extensive list of function calls to quickly and easily integrate the bc635PCIe card into your target environment. For Windows, an additional clock utility program, TrayTime, is provided that can be used to automatically update the host computer's clock.

The bc635PCIe firmware is easily field-upgradeable.

**Control Panel Interface**

#### **Product Includes**

This product also includes a bc635PCle time and frequency processor board, standard height and low-profile cover plates, one-year warranty, a PCle user guide CD, and a Windows, Linux, and Solaris SDK/driver software CD.

# **Ordering Information**

bc635PCIe PCIe time and frequency processor

bc635PCIe-OCXO PCIe time and frequency processor with oven controlled crystal oscillator for extended holdover connector accessories that can be ordered.

- D connector to x5-BNCs adapter (provides TC in, TC out, 1PPS out, event in, periodic out) BC11576-1000

- D connector to x5-BNCs adapter with 1PPS in (provides TC in, TC out, 1PPS in, 1PPS out, event in) BC11576-9860115

- D connector to x6-BNCs adapter (provides TC in, TC out, 1PPS in, 1PPS out, event in, DCLS out) PCI-BNC-CCS

- 203, Ansal Chamber-II, 6, Bhikaji Cama Place, New Delhi-110066

- 9 +91 11 26700500/26103358

6 +91 11 26183229

8 +91-9212605204

- marketing@savitritelecom.com

@2022 Savitri Telecom Services Product specifications and descriptions in this document are subject to change without notice. @1022STSACds-TFP-001